Maple bus

The Maple bus is the communications bus the Dreamcast uses to connect controllers and other related peripherals. It is a symmetrical serial protocol.

Hardware Overview

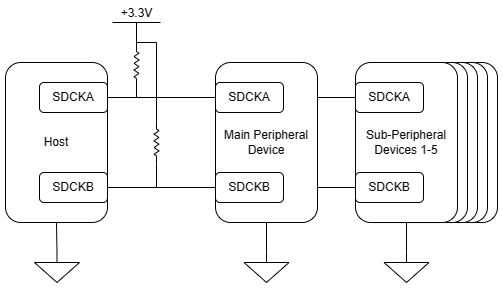

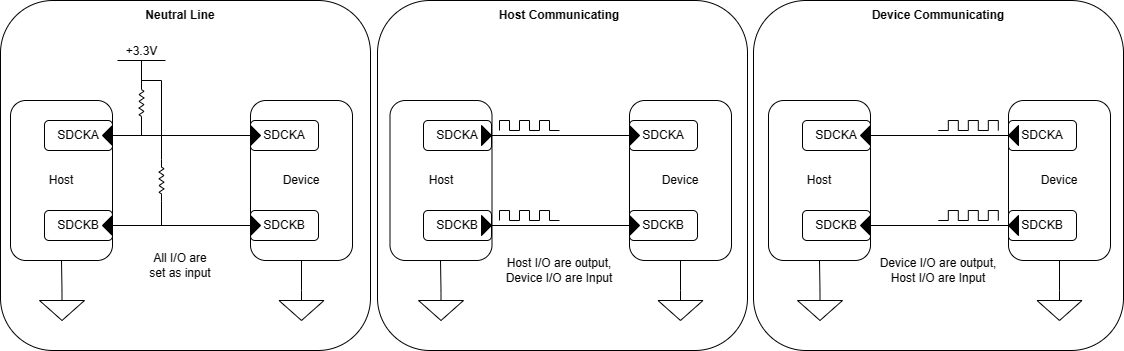

A Maple Bus consists of 2 signal/clock lines that are labeled SDCKA and SDCKB. Hardware on the Maple Bus consists of one host, zero or one main peripheral, and zero to five sub-peripherals. The only difference between a main peripheral and a sub-peripheral is that a main peripheral communicates to the host what sub-peripherals are attached during normal communication. The main peripheral is something like a Dreamcast controller, and the sub-peripherals are things like a VMU, rumble pack, and microphone. The host and all connected peripheral devices communicate on the same 2-line Maple Bus.

- Both lines on the Bus are pulled HIGH through weak pullup resistors

- Only one connected component on the bus may communicate at a time

- During communication, a device should not drive both lines HIGH for very long to prevent a downstream device from thinking the bus is free

- Before a component starts communicating, it must verify the bus is neutral for a sufficient amount of time

- A peripheral device will only communicate 1 packet of data in response to a request from the host

Maple Bus Signals

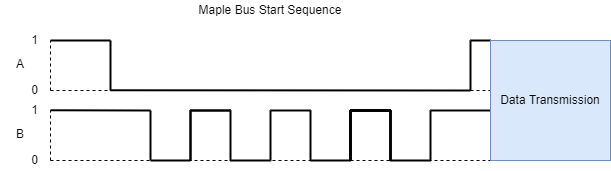

Start Sequence

Every packet begins with a start sequence.

- SDCKA is brought LOW

- SDCKB is toggled 4 times

- SDCKA is then brought back HIGH to complete the sequence

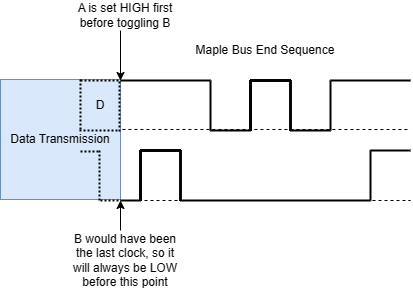

End Sequence

Every packet is completed with an end sequence to commit the data to the target component.

- SDCKA is brought HIGH

- SDCKB is toggled HIGH then LOW

- SDCKA is toggled 2 times

- SDCKB is brought back HIGH to complete the sequence

Data Bits

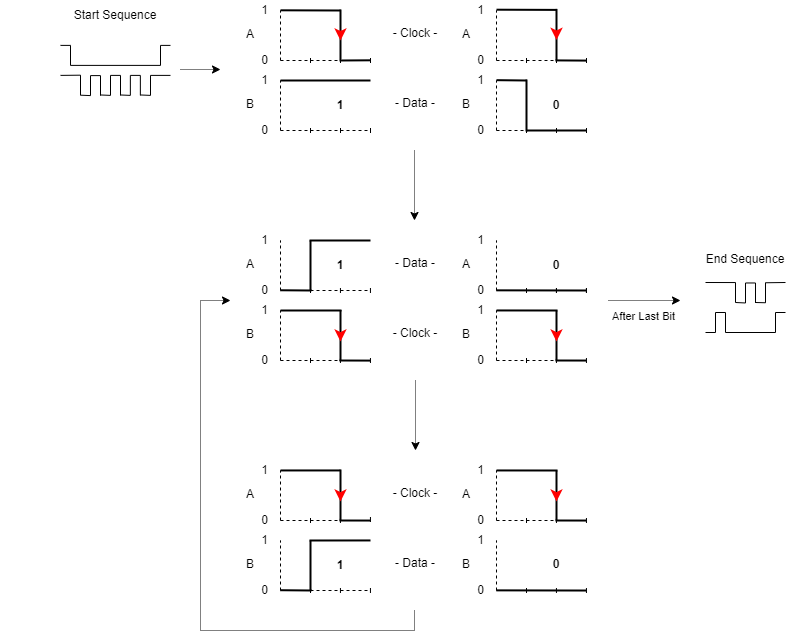

For each bit, one line of the maple bus acts as a clock while the other is the data to be sampled. A data bit is clocked when the designated clock line transitions from HIGH to LOW. The two lines trade their function after each bit. Line **A** acts as clock and **B** acts as data for the first bit. Line **B** acts as clock and **A** acts as data for the next bit. Line **A** acts as clock again for the bit after that. The pattern repeats until all data is transmitted.

Each state transition can be broken down into 3 phases:

- Phase 1 - Clock Conditioning: Bring clock HIGH and keep data at the state it was previously

- Phase 2 - Data Conditioning: Transition the data bit to the target value

- Phase 3 - Clocking: Bring clock LOW in order to have the data bit sampled

There are a total of 6 types of state transitions, depending on what the previous phase was. A depiction of state transitions can be seen in the image below.

Notice that each line, A & B transitions states in a staggard pattern. On the Dreamcast, each "phase" lasts about 160 nanoseconds which means each bit can be transmitted in about 480 nanoseconds. Because of the staggard pattern, the minimum time between one edge and the next on each line is the sum of the time of 2 phases which is about 320 nanoseconds on the Dreamcast.

Dreamcast controllers usually transmit a little slower with each phase lasting about 250 nanoseconds with about 110 microsecond delays between each 3 word chunk after the first frame word.